Leicht gemacht: Dyplo 2.0 beschleunigt FPGA-Programmierung

Aries Embedded bietet neueste Version des FPGA-Tools von Topic für eine flexiblere Nutzung der Miami FPGA-Module

Aries Embedded präsentiert neue Version des FPGA-Tools Dyplo 2.0 von Topic für mehr Leistung (Bildqu

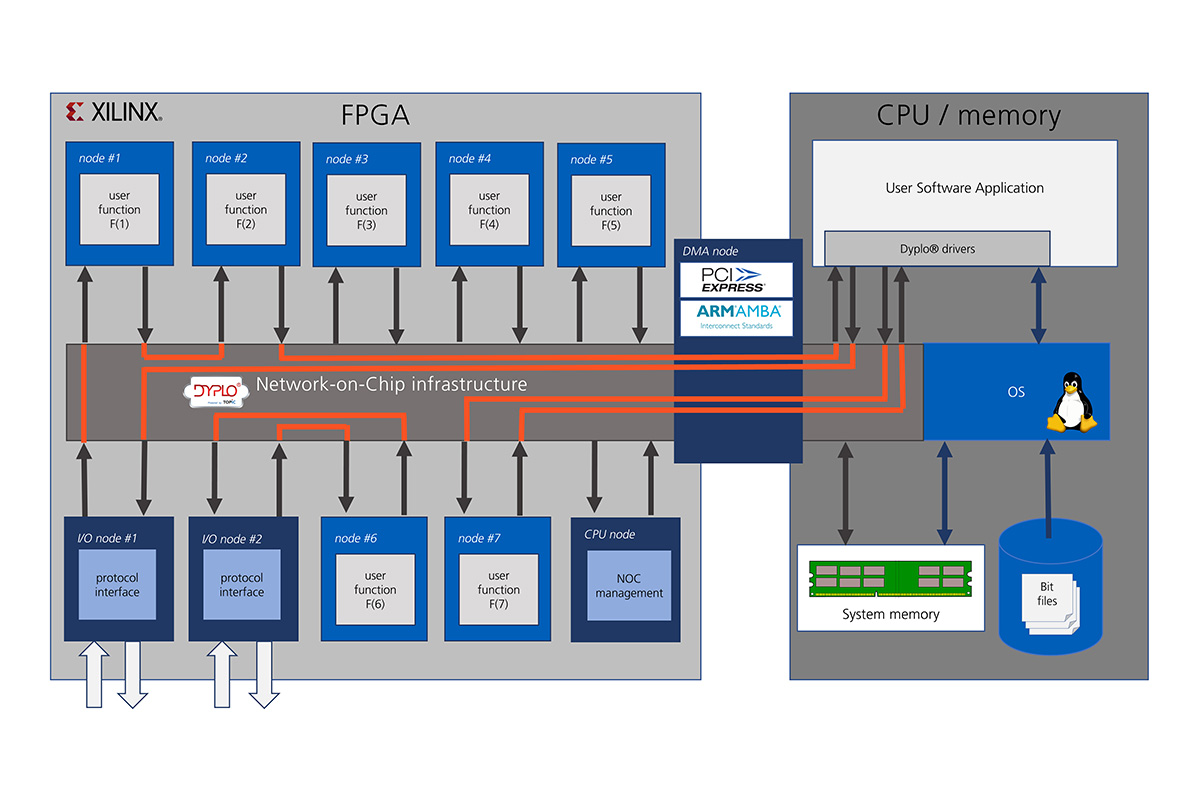

Aries Embedded präsentiert neue Version des FPGA-Tools Dyplo 2.0 von Topic für mehr Leistung (Bildqu(firmenpresse) - ARIES Embedded, Spezialist für Embedded-Services und -Produkte, vereinfacht und beschleunigt mit der neuen Version des FPGA-Tools Dyplo 2.0 von Topic Embedded Systems die Verwendung der Miami FPGA-Module. Dyplo baut auf der Xilinx Dynamic Function Exchange (DFX) Technologie und High-Level-Synthese auf. "Das Update von Topics Dynamic Process Loader ermöglicht eine flexiblere Konfiguration von FPGAs sowie die Verwendung von kleineren FPGAs und spart damit Energie bei potentiell höherem Durchsatz", erläutert Andreas Widder, Geschäftsführer von Aries Embedded. "Dyplo lässt sich als Tool ähnlich wie OpenCL verwenden. Weitere Features wie die partielle Rekonfiguration des FPGAs oder leistungsfähige DMA-Zugriffe beim Betrieb einer PCI-Express-Schnittstelle helfen den Anwendern, spezielle IP als Accelerator oder Algorythmik zu entwickeln." Die Einsatzbereiche reichen von Industrie, Telekommunikation, Luftfahrt, Raumfahrt und Medizintechnik bis zur Sicherheitstechnik.

Software-Update für hohe Leistung und Flexibilität

Die neue Version Dyplo 2.0 unterstützt die neuesten Xilinx-Bausteine, einschließlich der Alveo-Boards und Cloud-basierten Systeme. Eine wesentliche Verbesserung ist die Vergrößerung der Busbreite von 32 auf 64 Bit. Zudem unterstützt das Update niedrige Latenzen und hohen Datendurchsatz, die zum Beispiel bei Applikationen für das Image Processing von 4K-Videos nötig sind. Auch die Leistung und Flexibilität der DMA-Engine wurde weiter verbessert, um den anspruchsvollen Designanforderungen heutiger Systeme gerecht zu werden. Das leistungsfähige Tool bietet bei Bedarf rekonfigurierbare Funktionsblöcke auf dem FPGA, die die flexible Verwendung des FPGA ermöglichen. Damit lässt sich dieselbe FPGA-Logik für mehrere Funktionen wiederverwenden, was zu einer kleineren FPGA-Größe und damit geringerem Stromverbrauch führt.

Einfacher Projekteinstieg mit Dyplo Entwicklungskit

Für den einfachen und schnellen Einstieg in FPGA-Projekte stellt Aries Embedded das Dyplo Entwicklungskit (DDK) bereit. Das Kit besteht aus einem Alveo U50 Board, auf dem das Dyplo 2.0 Framework läuft. Dieses kann mit den Betriebssystemen Linux und Windows verwendet werden. Der Support von Dyplo 2.0 für Xilinx Alveo-Boards macht es sehr einfach, die FPGA-Technologie von Xilinx in Cloud- oder Edge-basierte Lösungen einzubinden.

Weitere Informationen:

https://www.aries-embedded.com/evaluation-kit/tools/dyplo-dynamic-process-loaderWeitere Infos zu dieser Pressemeldung:

Themen in dieser Pressemitteilung:

aries-embedded

topic-embedded

xilinx

dyplo

embedded-system

fpga

software

betriebssystem

network

on

chip

high

speed

industrie

telekommunikation

luftfahrt

raumfahrt

medizintechnik

Unternehmensinformation / Kurzprofil:

Über ARIES Embedded

ARIES Embedded bietet kundenspezifische Hardware- und Software-Entwicklung und Standardprodukte für Industrie und Landwirtschaft. Der Schwerpunkt des 2001 gegründeten Embedded-Spezialisten mit Sitz in Fürstenfeldbruck, Deutschland, liegt auf der FPGA-Technologie und Open-Source-Software. Das Angebot umfasst modulare Systeme für den flexiblen und schnellen Einsatz in funktionalen Prototypen, Pilotserien und der Serienproduktion. Im Kundenauftrag passt ARIES Embedded Standardprojekte individuell an Projektanforderungen an.

ahlendorf communication

Mandy Ahlendorf

Hermann-Roth-Straße 1

82065 Baierbrunn

ma(at)ahlendorf-communication.com

+49 89 41109402

www.ahlendorf-communication.com

Datum: 12.10.2021 - 15:05 Uhr

Sprache: Deutsch

News-ID 1933096

Anzahl Zeichen: 2846

Kontakt-Informationen:

Ansprechpartner: Andreas Widder

Stadt:

Fürstenfeldbruck

Telefon: +49 8141 36 367 0

Kategorie:

Elektro- und Elektronik

Diese Pressemitteilung wurde bisher 299 mal aufgerufen.

Die Pressemitteilung mit dem Titel:

"Leicht gemacht: Dyplo 2.0 beschleunigt FPGA-Programmierung"

steht unter der journalistisch-redaktionellen Verantwortung von

ARIES Embedded GmbH (Nachricht senden)

Beachten Sie bitte die weiteren Informationen zum Haftungsauschluß (gemäß TMG - TeleMedianGesetz) und dem Datenschutz (gemäß der DSGVO).

ARIES Embedded, Spezialist für Embedded-Services und -Produkte, präsentiert mit dem MSRZG3E ein neues OSM-konformes System-in-Package (SiP) auf Basis des Renesas RZ/G3E Mikroprozessors (MPU). Der RZ/G3E kombiniert einen Quad-Core-Arm® Cortex®-A55, einen Cortex-M33-Echtzeitkern und die Ethos™-U

ARIES Embedded stellt SMARC®-kompatible SoM MRZG2LS und MRZV2LS vor ...

ARIES Embedded, Spezialist für Embedded-Services und -Produkte, präsentiert die neuen SMARC®-kompatiblen System-on-Module (SoM) MRZG2LS und MRZV2LS. Die SoM basieren auf der Architektur der Renesas RZ-Familie und bieten eine hohe Leistungsfähigkeit für Embedded-Systeme. Der RZ/G2L-Mikroprozesso

ARIES Embedded begrüßt Emcraft Systems im Partnernetzwerk ...

Mit dem neuen Vertriebspartner Emcraft Systems (US-Anbieter von Embedded-Systemen) baut ARIES Embedded (Spezialist für Embedded-Services und -Produkte) seine Aktivitäten auf dem US-Markt aus und begegnet der steigenden Nachfrage. "Durch unsere Kooperation mit Emcraft Systems erhalten US-Kunde

Weitere Mitteilungen von ARIES Embedded GmbH

Mobiles ZfP-System von AT– Automation Technology wird zum internationalen Branchen-Allrounder ...

br /> C-CheckIR ermöglicht zerstörungsfreie Prüfung von Faserverbundstoffen vor Ort Messung innerhalb weniger Sekunden sowohl an vertikalen als auch an horizontalen Flächen Kontinuierlich neue Einsätze weltweit durch flexible Anpassung an Material, Messgröße und Messtechnik Branchenübergr

Lichtlösungen für präzises, schnelles Eingreifen auf der IMC-Station ...

Das Klinikum Garmisch-Partenkirchen widmet sich mit 1500 hochqualifizierten Mitarbeitern in 18 Spezialgebieten jährlich 23.000 stationären und 45.000 ambulanten Patienten. 2021 wurden die Kapazitäten ausgeweitet; eine neue Intermediate Care-Station an das bestehende Klinikgebäude angebaut.

Praxisbericht: Wie NB-IoT zu besserer Luftqualität in geschlossenen Räumen beitragen kann ...

Gerade in den vergangenen fast zwei Jahren wurde die elementare Bedeutung von gut belüfteten Räumen und einem entsprechenden Raumklima besonders deutlich. Mit Hilfe der NB-IoT-Technologie gelang es one:solutions und Magenta eine Lösung zu entwickeln, wie Sie die Raumluft in Büros, Geschäftsloka